# RF5601

4.9GHz to 5.85GHz Low Noise Amplifier with Bypass

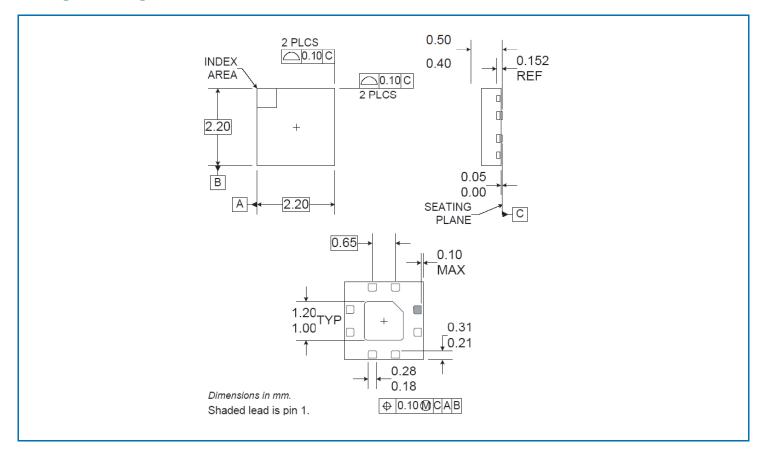

The RF5601 is a high performance Low Noise Amplifier designed for 802.11a/n/ac applications and other portable consumer electronics. The small form factor and high level of integration (input and output match, internal DC blocking capacitors) reduces the number of external components keeping cost down and minimizing layout area for implementation. The RF5601 is featured in a 2.2mm x 2.2mm x 0.5mm 8-pin QFN package.

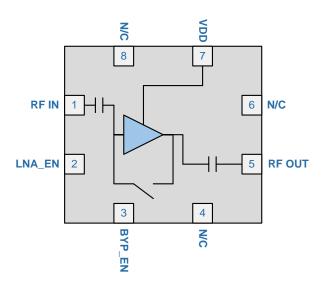

Functional Block Diagram

# **Ordering Information**

| RF5601        | Standard 25 piece bag                           |

|---------------|-------------------------------------------------|

| RF5601SR      | Standard 100 piece reel                         |

| RF5601TR7     | Standard 2500 piece reel                        |

| RF5601PCK-410 | Fully populated evaluation board w/ 5 piece bag |

Package: QFN, 8-pin, 2.2mm x 0.5mm

#### **Features**

- Single Supply Voltage 2.3V to 4.8V

- 1.8 dB Noise Figure

- 12 dB Typical Gain

- 5dB IL in Bypass Mode

## **Applications**

- 802.11a/n/ac WiFi Applications

- Consumer Electronics

- Mobile Devices

- Gaming

- General Purpose 5GHz LNA

## **Absolute Maximum Ratings**

| Parameter                     | Rating      | Unit |

|-------------------------------|-------------|------|

| DC Supply Voltage             | 5.5         | V    |

| RF Input Power                | +5*         | dBm  |

| Operating Ambient Temperature | -40 to +85  | °C   |

| Storage Temperature           | -40 to +150 | °C   |

| Moisture Sensitivity          | MSL2        |      |

<sup>\*</sup>Note: Maximum input power with a 50Ω load in High Gain mode.

Caution! ESD sensitive device.

RFMD Green: RoHS status based on EU Directive 2011/65/EU (at time of this document revision), halogen free per IEC 61249-2-21, < 1000ppm each of antimony trioxide in polymeric materials and red phosphorus as a flame retardant, and <2% antimony in solder.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

## **Nominal Operating Parameters**

|                                      | Specification |      |      | 11.24 |                                                                                                                                                                               |  |  |  |

|--------------------------------------|---------------|------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Parameter                            | Min           | Тур  | Max  | Unit  | Condition                                                                                                                                                                     |  |  |  |

| Typical Conditions                   |               |      |      |       | Temp = 25°C, V <sub>DD</sub> = 3.3V, LNA_EN = 3.3V, BYP_EN = 3.3V in high<br>gain mode, BYP_EN = 0V in Bypass mode,<br>Frequency = 4.9 GHz to 5.85 GHz unless otherwise noted |  |  |  |

| Frequency                            | 4.9           |      | 5.85 | GHz   |                                                                                                                                                                               |  |  |  |

| DC Voltage Supply (V <sub>DD</sub> ) | 2.3           | 3.3  | 4.8  | V     |                                                                                                                                                                               |  |  |  |

| LNA_EN Low                           |               |      | 0.2  | V     | LNA OFF. See logic table for additional control settings.                                                                                                                     |  |  |  |

| LNA_EN High                          | 2.3           | 3.3  | VDD  | V     | LNA ON. BYP_EN control must be high simultaneously for High Gain Mode. See control table.                                                                                     |  |  |  |

| BYP_EN Low                           |               |      | 0.2  | V     | Bypass mode ON. See logic table for more details.                                                                                                                             |  |  |  |

| BYP_EN High                          | 1.8           | 3.3  | VDD  | V     | Bypass mode OFF. See logic table for more details.                                                                                                                            |  |  |  |

| LNA Current                          |               |      |      |       |                                                                                                                                                                               |  |  |  |

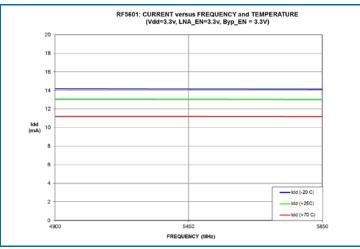

| LNA I <sub>DD</sub>                  |               | 12   | 17   | μΑ    | LNA in "On" state, over full DC supply range, LNA_EN supply range and over normal operating temperature range (-20°C to 75°C)                                                 |  |  |  |

|                                      |               | 3    | 5    | μΑ    | LNA in "Off" state, V <sub>DD</sub> = 0V; LNA_EN = 0V, BYP_EN = 0V                                                                                                            |  |  |  |

| LNA Enable                           |               | 2    | 10   | μA    | V <sub>DD</sub> = 2.3V to 4.8V, LNA_EN = 2.3V to 4.8V, over full frequency range, and over normal operating temperatures - 20°C to +75°C                                      |  |  |  |

| High Gain Mode                       |               |      |      |       |                                                                                                                                                                               |  |  |  |

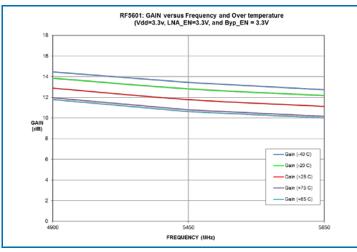

| Gain                                 | 9             | 12   | 15   | dB    | Over full $V_{DD}$ and LNA_EN ranges, over frequency and over full temperature range from -40°C to +85°C                                                                      |  |  |  |

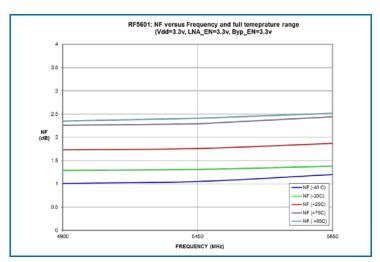

| Noise Figure                         |               |      |      |       |                                                                                                                                                                               |  |  |  |

| Hi Gain Mode                         |               | 1.8  | 2.6  | dB    | Over full V <sub>DD</sub> , LNA_EN, and BYP_EN voltages, over frequency and normal operating temperatures (-20°C to +75°C)                                                    |  |  |  |

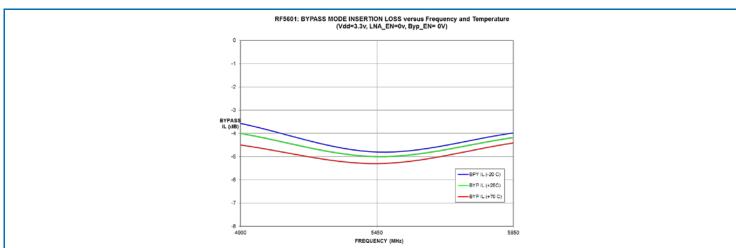

| Bypass Mode                          |               |      |      |       |                                                                                                                                                                               |  |  |  |

| Insertion Loss                       |               | 5.0  | 7.0  | dB    |                                                                                                                                                                               |  |  |  |

| Passband Ripple                      | -1.0          |      | +1.0 | dB    | LNA is in High Gain mode, over full frequency range, over full $V_{\text{DD}}$ and LNA_EN voltage range                                                                       |  |  |  |

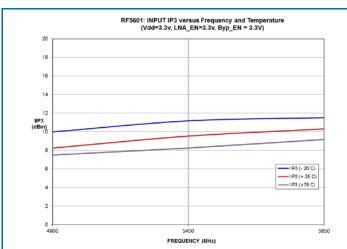

| Input IP3                            |               | +9   |      | dBm   | High Gain mode                                                                                                                                                                |  |  |  |

| RF Port Return Loss                  | 9.6           | 15.0 |      | dB    | Input and output. No external matching.                                                                                                                                       |  |  |  |

| Parameter                      | Specification |     |     | Unit | Condition                                                                                                                                                       |  |  |

|--------------------------------|---------------|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| raiailletei                    | Min           | Тур | Max | Onne | Condition                                                                                                                                                       |  |  |

| Typical Conditions (continued) |               |     |     |      | Temp = 25°C, VDD = 3.3V, LNA_EN = 3.3V, BYP_EN = 3.3V in hi<br>gain mode, BYP_EN = 0V in Bypass mode,<br>Frequency = 4.9 GHz to 5.85 GHz unless otherwise noted |  |  |

| RF Port Impedance              |               | 50  |     | Ω    | Input and output. No external matching                                                                                                                          |  |  |

| LNA Turn On/Off Time           |               | 100 | 160 | nSec |                                                                                                                                                                 |  |  |

| ESD                            |               |     |     |      |                                                                                                                                                                 |  |  |

| Human Body Model               | 500           |     |     | V    | EIA/JESD22-114A RF pins                                                                                                                                         |  |  |

|                                | 500           |     |     | V    | EIA/JESD22-114A DC pins                                                                                                                                         |  |  |

| Charge Device Model            | 350           |     |     | V    | JESD22-C101C all pins                                                                                                                                           |  |  |

# **Control Logic Table**

| Mode                  | Controls |        |        |  |  |  |  |

|-----------------------|----------|--------|--------|--|--|--|--|

|                       | VDD      | LNA_EN | BYP_EN |  |  |  |  |

| High Gain             | High     | High   | High   |  |  |  |  |

| Bypass Mode           | High     | Low    | Low    |  |  |  |  |

| Undefined*            | High     | High   | Low    |  |  |  |  |

| High In/Out Isolation | High     | Low    | High   |  |  |  |  |

<sup>\*</sup>This state is not recommended

#### **Plots**

4 of 9

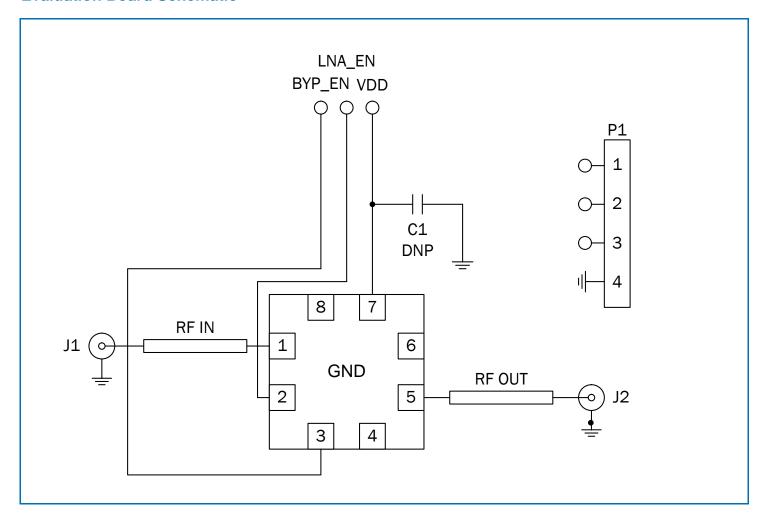

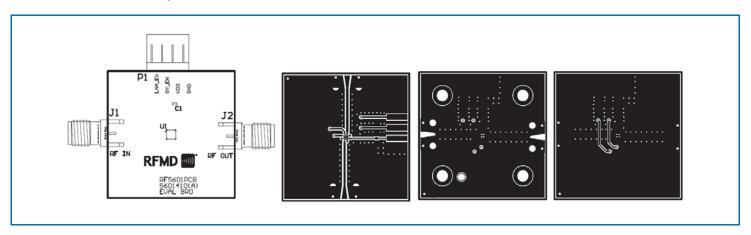

#### **Evaluation Board Schematic**

# **Evaluation Board Layout**

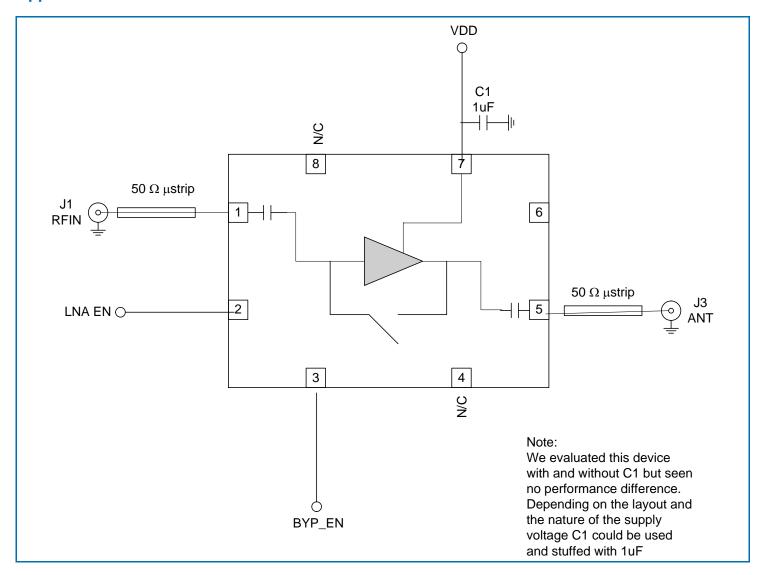

# Application Schematic – 4.9GHz to 5.85GHz

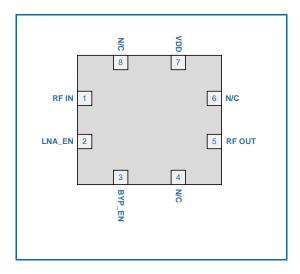

#### **Pin Out**

# **Package Drawing**

# **Pin Names and Descriptions**

| Pin      | Name   | Description                                                                                                |  |  |  |  |

|----------|--------|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1        | RF IN  | RF Input. Input is matched to $50\Omega$ and DC block is provided internally.                              |  |  |  |  |

| 2        | LNA_EN | LNA Enable. Please see truth table for operation.                                                          |  |  |  |  |

| 3        | BYP_EN | Bypass Enable. Please see truth table for operation.                                                       |  |  |  |  |

| 4        | NC     | No Connect.                                                                                                |  |  |  |  |

| 5        | RF OUT | RF Output. Output is matched to $50\Omega$ and DC-block is provided internally.                            |  |  |  |  |

| 6        | NC     | No Connect.                                                                                                |  |  |  |  |

| 7        | VDD    | Supply voltage for the LNA circuit.                                                                        |  |  |  |  |

| 8        | NC     | No Connect                                                                                                 |  |  |  |  |

| Pkg Base |        | The center metal base of the QFN package provides DC and RF ground as well as heat sink for the amplifier. |  |  |  |  |

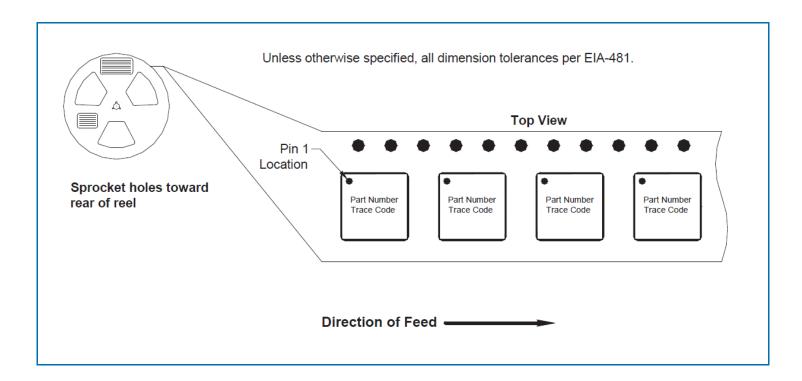

## **Tape and Reel**

Carrier tape basic dimensions are based on EIA 481. The pocket is designed to hold the part for shipping and loading onto SMT manufacturing equipment, while protecting the body and the solder terminals from damaging stresses. The individual pocket design can vary from vendor to vendor, but width and pitch will be consistent.

Carrier tape is wound or placed onto a shipping reel either 330 mm (13 inches) in diameter or 178 mm (7 inches) in diameter. The center hub design is large enough to ensure the radius formed by the carrier tape around it does not put unnecessary stress on the parts.

Prior to shipping, moisture sensitive parts (MSL level 2a-5a) are baked and placed into the pockets of the carrier tape. A cover tape is sealed over the top of the entire length of the carrier tape. The reel is sealed in a moisture barrier ESD bag with the appropriate units of desiccant and a humidity indicator card, which is placed in a cardboard shipping box. It is important to note that unused moisture sensitive parts need to be resealed in the moisture barrier bag. If the reels exceed the exposure limit and need to be rebaked, most carrier tape and shipping reels are not rated as bakeable at 125°C. If baking is required, devices may be baked according to section 4, table 4-1, of Joint Industry Standard IPC/JEDEC J-STD-033.

The table below provides useful information for carrier tape and reels used for shipping the devices described in this document.

| RFMD Part Number | Reel<br>Diameter<br>Inch (mm) | Hub<br>Diameter<br>Inch (mm) | Width<br>(mm) | Pocket Pitch<br>(mm) | Feed   | Units per<br>Reel |

|------------------|-------------------------------|------------------------------|---------------|----------------------|--------|-------------------|

| RF5601TR7        | 7 (178)                       | 2.4 (61)                     | 12            | 4                    | Single | 2500              |